# Supplemental Pod Information for 9100A/9105A Users

## MANUAL UPDATE PACKAGE

ISSUE NO: 1

DATE: 2/89

This Manual Update Package contains information necessary to ensure the accuracy of the following manual:

## MANUAL

Title:

Supplemental Pod Information for 9100A/9105A Users

Print Date: Rev. - Date:

July 1987 2, 3/88

## PAGE EFFECTIVITY

Page No. Print Date

1 2/89

#### Supplemental Pod Information

|  | 1802 | POD |  |

|--|------|-----|--|

|--|------|-----|--|

## POD CONNECTION TO 9100 SERIES MAINFRAMES

Connect the pod cable with the 25-pin connector to the pod port on the side of the mainframe. The cable with the 9-pin connector is not used with 9100 Series products. Secure the connector using the slide locking collar.

All 9100 Series probe stimulus/response functions can be used for the UUTs with Vcc of 5V (the probe thresholds must be set to CMOS).

#### NOTE

The 9100 Series probe may be used as a measurement device for UUTs with Vcc greater than 5V if UUT logic low is below 0.8V. Again, the probe thresholds must be set to CMOS. If the probe is used in this manner, be aware that the thresholds of the probe do not match thresholds of typical CMOS devices when Vcc is above 5V. The output functions of the probe cannot be used for UUTs with Vcc greater than 5V.

# Supplemental Pod Information

## TABLE OF CONTENTS

|             | TITLE    | PAGE                                    |                         |

|-------------|----------|-----------------------------------------|-------------------------|

| Oper<br>Pod | oduction | Int                                     | roduction-2 roduction-4 |

| 1802        | Pod      | • • • • • • • • • • • •                 | 1802-1                  |

| 6502        | Pod      |                                         | 6502-1                  |

| 6800        | Pod      | · • • • • • • • • • • • • • • • • • • • | 6800-1                  |

| 6802        | Pod      |                                         | 6802-1                  |

| 6809        | Pod      |                                         | 6809-1                  |

| 6800        | 0 Pod    | · • • • • • • • • • • • • • • • • • • • | 68000-1                 |

| 8080        | Pod      | • • • • • • • • • • • •                 | 8080-1                  |

| 8085        | Pod      | • • • • • • • • • • • •                 | 8085-1                  |

| 8048        | Pod      |                                         | 8048-1                  |

| 8051        | Pod      |                                         | 8051-1                  |

| 8086        | Pod      |                                         | 8086-1                  |

| 8088        | Pod      |                                         | 8088-1                  |

| 8018        | 6 Pod    |                                         | 80186-1                 |

| 8018        | 8 Pod    |                                         | 80188-1                 |

| 9900        | Pod      |                                         | 9900-1                  |

| Z80         | Pod      |                                         | Z80-1                   |

| Z800        | O Pod    |                                         | Z8000-1                 |

#### INTRODUCTION

#### Pods Supported

This manual provides information to support use of the Interface Pods listed below with 9100 series testers. The manual is a supplement to the Instruction Manual for each Pod.

| 1802  | 6502  | 6800 | 6802 | 6809  | 68000 |

|-------|-------|------|------|-------|-------|

| 8080  | 8085  | 8048 | 8051 | 8086  | 8088  |

| 80186 | 80188 | 9900 | 7.80 | 78000 |       |

## Multiple Databases per Pod

Many Fluke microprocessor interface pods support more than one microprocessor type. These pods fall into two types. The first type enters a mode depending upon the type of microprocessor installed in the pod and/or the configuration of switches on the pod. The second type of pod is general enough in its operation that it can emulate several processor types without knowing the specific type on the UUT.

The first type of pod reports to the mainframe which mode it is in and the mainframe automatically loads a database appropriate to that mode.

The mainframe also automatically loads a database for the second type of pod, but this may not be the database that enables the pod to most closely emulate the processor type. A keystroke method is available to choose a specific database. To do this, press the SETUP MENU key on the front panel of the 9100 series tester. Then select the POD NAME softkey. You can enter an alphanumeric value for the name of the database to be loaded and used with the pod that is installed. Further information about valid database names for each pod may be found in the sections for pods that support this feature.

#### OPERATOR'S INFORMATION

#### Reading the Database Version Number

Pod databases are disk files in the 9100 series Mainframe that contain information to determine the pod's interface to the rest of the system. To read the version number of the database from the front panel, press the SETUP, ->, and SOFT KEYS keys, the POD\_NAME softkey, then the ENTER key. After a short disk operation, the front panel will display PODFILE = xxxxxx.# where xxxxxx is the pod database name and # is the revision level of that database.

## Understanding 9100 Pod Self Test Return Codes

9100 series mainframe pod test algorithms are improved over those of 9000 series mainframes. Hence, the error codes returned by the 9100 series mainframes have different meanings. Table 1 details the steps that the 9100 takes in testing pods and their corresponding error codes.

## NOTES FOR TABLE 1 (on next page):

- A = UUT power sensing circuit fault.

- B = Control line(s) cannot be driven.

- C = Address line(s) cannot be driven.

- D = Wrong data read.

- E = Data line(s) cannot be driven.

- F = Forcing or interrupt line buffer(s) or associated logic faulty.

maxdata = FF for 8-bit interface pods.

FFFF for 16-bit interface pods.

- N = the number of enableable lines in the pod.

- S = the number of address spaces in the pod.

Table 1. 9100 Pod Selftest Error Codes

| ERROR<br>CODE<br>(DECIMAL)                           |                                                                                                                                                                                                                                                                                       | <br>  POSSIBLE  <br> FAULTS WHEN  <br> ACTION FAILS  <br> |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 0000<br>  0001<br>  0002<br>  0003<br>  0004         |                                                                                                                                                                                                                                                                                       | A, B, C, E  <br>B                                         |

| 0005<br>0006<br>0007<br>0008                         | Readspecial addr 0000F00F.   Writespecial addr 00000001, data FFFFFFFE AND maxdata   Writespecial addr 00000002, data FFFFFFFD AND maxdata   Writespecial addr 00000004, data FFFFFFFB AND maxdata   Writespecial addr 00000008, data FFFFFFF7 AND maxdata                            | A, B, C, E  <br>A, B, C, E                                |

| 0010                                                 | Writespecial addr 00000010, data FFFFFFFF AND maxdata   Writespecial addr 00000020, data FFFFFFDF AND maxdata   Writespecial addr 00000040, data FFFFFFBF AND maxdata   Writespecial addr 00000080, data FFFFFF7F AND maxdata                                                         | A, B, C, E  <br>A, B, C, E  <br>A, B, C, E                |

| 0035<br>0036<br>0037<br>0038                         | V   V   Writespecial addr 10000000, data EFFFFFFF AND maxdata  Writespecial addr 20000000, data DFFFFFFF AND maxdata  Writespecial addr 40000000, data BFFFFFFF AND maxdata  Writespecial addr 80000000, data 7FFFFFFF AND maxdata  Enable first pod enableable line.                 | A, B, C, E  <br>A, B, C, E                                |

|                                                      | Enable second pod enableable line.                                                                                                                                                                                                                                                    | F  <br>                                                   |

| 0038+N                                               | (N defined in NOTES on previous page)<br> Write maxdata to high address of first address space. <br> (N defined in NOTES on previous page)<br>                                                                                                                                        | A, B, C, E  <br> <br>                                     |

|                                                      | Write maxdata to high address of last address space.  <br>(N and S defined in NOTES on previous page)                                                                                                                                                                                 | A, B, C, E                                                |

| 2002  <br>  2003  <br>  2004  <br>  2005  <br>  2006 | Pod is not in selftest socket.  Unexpected powerfail.  No powerfail when expected.  Pod not reporting ABORT when ABORT line toggled.  Pod reporting ABORT unexpectedly.  Pod drops dead unexpectedly.  Pod gives error setting enableable lines.  Pod gives error setting fault mask. |                                                           |

#### POD CALIBRATION

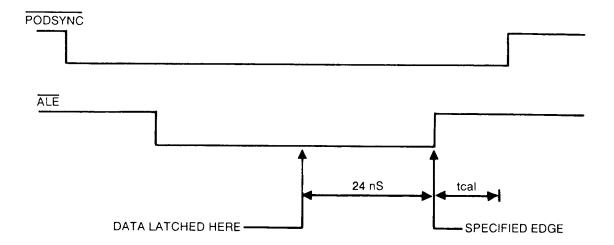

Calibration is the process by which the internal delay lines in the I/O module and Probe are adjusted to correctly line up, in time, the clock and data signals. (Data, in this context, refers to the signal to be sampled, be it address, data, etc.) To calibrate an I/O Module or Probe to a pod, for a particular pod sync mode, the user is prompted to probe a signal on the UUT. A particular edge on that signal is found by adjusting the delay lines in the I/O module or Probe relative to the internal PODSYNC signal. Once the edge is found, an offset is applied to that edge to determine just where in time the I/O module or Probe will latch data.

This manual lists the calibration data for each pod and sync mode. Following is an example for the imaginary xyz pod showing how the data is listed in the manual, and how this data would apply to real waveforms.

#### EXAMPLE:

In the imaginary xyz pod, Address sync is to be calibrated to the rising edge of the ~ALE line. For this example, valid address is best captured when sampled 24ns before the rising edge of ~ALE. The data would appear in the manual like this:

| SYNC MODE      | <br>  UUT SIGNAL<br> | <br>  EDGE OF SIGNAL<br> |       |

|----------------|----------------------|--------------------------|-------|

| <br>  ADDR<br> | ~ALE                 | <br>  RISING<br>         | -24ns |

The waveforms would look like this:

NOTE: In this manual, any active-low signal name starts with '~'.

If calibration is not performed, a default setting is used for tcal, (the location of the ~ALE signal relative to ~PODSYNC). The -24ns offset is applied to this setting. When calibration is performed, tcal is actually measured, and the default is replaced with the measured value. If the TL/1 function "getoffset" were executed after calibration, an offset of -24ns should be returned, (or a number near -24, reflecting the granularity of the hardware delay lines). If other offsets are desired, the TL/1 function "setoffset" can be used. See the description of setoffset and getoffset in the TL/1 documentation for exact syntax and details.

#### PROGRAMMER'S INFORMATION

#### Fault Masks

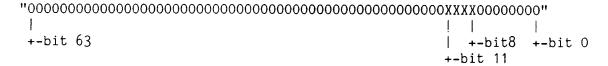

Faults raised during testing may be processed by fault handlers written in TL/1, or displayed on the front panel of the 9100 series mainframe. System fault names and arguments associated with those faults are listed in Appendix G of the TL/1 Reference Manual. Many of the faults listed there have an argument named mask, mask\_tied, mask\_low, or mask\_high. The format of these masks is a character string of exactly 64 ones (1) and zeros (0). "X" can be used for "don't care" bits. The rightmost position in the character string represents the least significant bit (LSB) position of the data item with the fault. The leftmost position of the string represents bit 63 of the data item with the fault.

The format of TL/1 fault masks follows directly from the model of a microprocessor used by the 9100 system. Processor signal lines are divided into address, data, status, and control groups. The format of each mask type is as follows:

Address, Data:

Bit positions map starting from MSB to LSB of mask. Bits beyond the processor bus width are unused.

Status, Control: Bit positions map directly from the pod underside decal or from the Status and Control Line Bit Assignment table in the pod manual. Other bits are unused.

Exceptions to this general fault mask structure are covered in the sections for the 8048, 8051, 80186, and 80188 pods.

Because the mainframe generates different fault masks (Data, Address, Control, or Status) depending on the type of fault, the meaning associated with a particular position changes from type to type. For instance, in the 68000 pod, bit 1 can mean either "BR fault (for status faults), ~VMA fault (for control faults), data bit 1 fault (for data faults), or address bit 1 fault (for address faults), depending on what type of fault occurred.

Table 2 lists the TL/1 fault masks for the 68000 pod.

Table 2. Bit Positions for 68000 Pod Fault Masks

| BIT<br>POSITION                                                                                | ADDRESS<br>MASK                                                   | DATA<br>MASK                                                 | STATUS<br>MASK                                                                                 | CONTROL MASK                                                                            |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | AO A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17     | D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 unused | THALT  BR BGACK BERR RESET  VPA DTACK PWR FAIL IPLO IPL1 IPL2 Intr vector note 1 note 2 unused | THALT  THALT  WMA  BG  unused  RESET  FCO  FC1  FC2  LDS  UDS  WDS  AS  E  unused  .  . |

| 18<br>19<br>20<br>21<br>22<br>23<br>24<br>:                                                    | A18<br>  A19<br>  A20<br>  A21<br>  A22<br>  A23<br> <br>  unused | .<br>  .<br>  .<br>  unused<br> <br>  unused                 | .<br>  .<br>  .<br>  .<br>  unused<br> <br>  unused                                            | .<br>  .<br>  .<br>  unused<br> <br>  unused                                            |

#### NOTES:

- 1. Neither ~DTACK nor ~VPA asserted.

- 2. Both ~DTACK and ~VPA asserted.

When testing within a fault handler, often only a particular fault is of interest. To do this, the fault mask can be compared against a string of ones, zeros, and Xs. As an example, suppose that only bit 3 is of interest. The comparison might be done something like this:

testmask = "XXXXX ... XXX1XXX"

if (mask = testmask) then ...

where the one is in the fourth position from the right (bit 3). The Xs cause any other fault to be temporarily ignored in the comparison. Other individual faults can be tested by changing the testmask string.

#### Examples of Fault Masks

end EXAMPLE1

The following examples show how fault masks are used to handle specific types of faults.

#### EXAMPLE : Forcing Line Fault Handlers

```

handle pod_forcing_active ( mask )

declare string mask

! Turn off reporting of forcing line faults if one is reported.

if (mid str mask, from 62, length 1) = "1" then

podsetup 'report forcing' "off"

end if

end pod_forcing_active

read addr 0

```

## EXAMPLE : Enableable Line Fault Handling

Each section in this manual contains information about the bit positions of the pod's enableable lines in the enableable line mask. Handling enableable line faults is exactly like handling other faults that use fault masks to report the bit position of the faulty line. For example, in the 6800 pod, there are three enableable lines; TSC in bit position 3, DBE in bit position 4, and "HALT in bit position 5 of the enableable line mask. The mask for a pod\_timeout\_enabled\_line fault for this pod would be of the format:

where the X would contain a 1 if TSC caused a pod timeout and 0 otherwise. Y would contain a 1 if DBE caused a pod timeout, etc. A fault handler could test for which enableable line caused the timeout (as was done in EXAMPLE1).

## Raising Built-in Faults from TL/1

TL/1 programs may raise system built-in faults. Information about system faults can be found in appendices G and H of the TL/1 Reference Manual. Raising built-in faults from a TL/1 program often requires that the fault mask format be passed as an argument to the fault statement. Care must be taken to ensure the mask is exactly 64 characters long. Program EXAMPLE2 shows how to raise a bus\_data\_low\_tied fault on data line D4. Assuming no handlers for this fault exist in the calling chain for EXAMPLE2, the fault would report on the 9100 series front panel just as if the front panel BUSTEST found D4 tied low. Other built-in faults may be raised in the same manner.

program EXAMPLE2

declare string fift6 0s

- - ! The program somehow decides that D4 is tied low. A fault is

- ! raised to indicate that fault.

! Raise the fault:

fault bus data low tied mask fift6 0s + "00010000"

- ! If no handlers for this fault are in the calling chain for

- ! EXAMPLE2, the 9100 series front panel will display:

- ! "data line D4 pin xx stuck low"

- ! The pin number xx in the fault message is pod-dependent.

end EXAMPLE2

## Pod-Specific Setup Information

Some pods have setup information that is only used for that pod. The TL/1 manual describes the podsetup command and gives examples of the podsetup command that can be used with any pod.

There are differences between the way the podsetup command works with the general setups and pod-specific setups. The following examples using the podsetup command are for the Z8000 pod. See the Z8000 section of this manual for a list of the setups that are available for that pod.

NOTE

TL/1 hexadecimal data requires a "\$" prefix character.

```

program SETUP

This program is a example of how to use the podsetup function

with pod-specific setup arguments (example pod-specific setup

!

information is from the Z8000 pod database).

IMPORTANT NOTES:

All character strings are case insensitive.

!

Standard (not pod-specific) setups use syntax with single

quoted arguments and double quoted values, eg.:

!

podsetup 'report intr' "off"

Pod specific setups either use a single single-quoted argument

or a single-quoted argument followed by a non-quoted value:

podsetup 'intr ack on'

•

podsetup 'seg reg ds' $F800

!

! Note, even though enableable status

! lines ~BUSRQ, ~WAIT are

! pod-specific, "enable" is not, so

! these use the "built-in" syntax.

podsetup 'enable ~busrq' "off"

podsetup 'enable ~wait' "off"

! These examples are all Z8000

! pod-specific.

podsetup 'trnsp rd high ad' $100F

podsetup '~mo sig state active'

podsetup 'refresh rate' $15

podsetup 'refresh status active'

! Note upper case works too.

podsetup 'TRNSP RD HIGH AD' $100F

podsetup '~MO SIG STATE ACTIVE'

podsetup 'REFRESH RATE' $15

podsetup 'REFRESH STATUS ACTIVE'

end SETUP

```

| <br>1802 | POD |  |

|----------|-----|--|

#### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

## POD ADDRESS SPACE OPTIONS AVAILABLE

The following pod address space options are available.

SPACE

MEMORY

I/0

#### POD-SPECIFIC SETUP INFORMATION

| POD SETUP              | RANGE/KEY | DEFAULT | POD MANUAL REFERENCE         |

|------------------------|-----------|---------|------------------------------|

| DMA_TRAP key QLINE key | ON/OFF    | ON      | See Section 4-21 and Tbl 4-2 |

|                        | ON/OFF    | OFF     | See Table 4-2                |

## AVAILABLE TL/1 SUPPORT PROGRAMS

NOTE

TL/1 hexadecimal data requires a "\$" prefix character.

CLR\_MBIO This program clears Multi-Bank I/O mode operation. For further information, see Section 4-19 and Table 4-2 in the 1802 pod manual.

Arguments: None.

Faults : None.

Returns : Nothing.

DMA\_IND This program returns the data from the most recent DMA IN operation, resets the DMA IN flag, and re-enables DMA operations. For more information, see Section 4-21 and Table 4-2 in the 1802 pod manual.

Arguments: None.

Faults: None.

Returns : The data from the most recent DMA  $\,$  IN operation that was

trapped by the pod.

DMA\_OUTD This program returns the data from the most recent DMA OUT operation, resets the DMA OUT flag, and re-enables DMA operations. For more information, see Section 4-21 and Table 4-2 in the 1802 pod manual.

Arguments: None.

Faults: None.

Returns: The data from the most recent DMA OUT operation that was trapped by the pod.

QWK\_IO\_R This program returns the data present at the passed I/O port number and places the pod in Quick Looping Read mode at that I/O port. For further information, see Section 4-15 through 4-20 and Table 4-2 of the 1802 pod manual.

Arguments: PORT - The port number at which the Quick Looping Read is to be performed. PORT may take values from 1 through 7.

Faults: test aborted

reason "Illegal port number".

The value of the PORT argument does not conform to the restrictions detailed above.

Returns: The data found at the passed port during the first cycle of the Quick Looping Read.

QWK\_IO\_W This program repeatedly writes the passed data to the passed I/O port number. For further information, see Section 4-15 through Section 4-20 and Table 4-2 in the 1802 pod manual.

Arguments: PORT - The port number at which the Quick Looping Read is to be performed. PORT may take values from 1 through 7.

DATA - The data that is to be written to the above I/O port. Any number between O and FF is a legal value for this argument.

Faults: test aborted

reason "Illegal port number".

The value of the PORT argument does not conform to the restrictions detailed above.

reason "Illegal data".

The value of the DATA argument does not conform to the restrictions detailed above.

Returns: Nothing.

QWK\_RD This program places the pod in Quick Looping read mode at the passed address. For further information about Quick Looping read mode, see Section 4-15 of the 1802 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping read. Any number between 0 and FFFF is a legal value for this argument.

Faults: test aborted

reason "Illegal address".

The ADDR argument does not conform to the specification detailed above.

Returns: The byte that is found at the address specified by the argument during the first UUT access of the Quick Looping read mode.

QWK\_WR This program may be used to put the pod in Quick Looping write mode using the data and address specified by the arguments. For further information on Quick Looping write mode, see Section 4-15 of the 1802 pod manual.

Arguments: ADDR - The address at which to perform the quick-looping write. Any number between 0 and FFFF is a legal value for this argument.

DATA - The data that is to be written to the address specified by the ADDR argument. Any number between 0 and FF is a legal value for this argument.

Faults: test aborted

reason "Illegal address".

The value of ADDR does not conform to the restrictions detailed above.

reason "Illegal data".

The value of DATA does not conform to the restrictions detailed above.

Returns : Nothing.

RD\_DMAR This program returns the current DMA register contents (16 bits). For further information, see Section 4-21 and Table 4-2 in the 1802 pod manual.

Arguments: None.

Faults: None.

Returns: The 16 bit-wide contents of the DMA register.

RD\_TRV This program returns the current value of the I/O transfer vector (16 bits). For further information, see Section 4-16 through Section 4-20 and Table 4-2 in the 1802 pod manual.

Arguments : None.

Faults: None.

Returns: The 16 bit-wide value of the I/O transfer vector.

SET\_DMAR This program sets the DMA register contents to the passed ADDR and writes the passed DATA to that address. For further information, see Section 4-21 and Table 4-2 in the 1802 pod manual.

Arguments: ADDR - This is the value to be loaded in the DMA register and the address to which the passed data will be written. This argument will take any value from 0 to FFFF.

DATA - This is the data to be written to the above address. Valid values for this argument are any number between 0 and FF.

Faults: test aborted

reason "Illegal address". The value of ADDR does not conform to the restrictions detailed above.

reason "Illegal data". The value of DATA does not conform to the restrictions detailed above.

Returns: Nothing.

SET\_MBIO This program sets up Multi-Bank I/O mode. After use of this program, every I/O operation will be preceded by a write of the passed DATA to the passed PORT. For further information, see Section 4-19 and Table 4-2 in the 1802 pod manual.

Arguments: PORT - This is the port that the bank selection data will be written to before each I/O operation.

Any number between 1 and 7 is a legal value for this argument.

DATA - The data to be written to the above port before each I/O operation. Any number between 0 and FF is a legal value for this argument.

Faults: test aborted

reason "Illegal port number".

The value of PORT does not conform to the restrictions detailed above.

reason "Illegal data".

The value of DATA does not conform to the restrictions detailed above.

Returns: Nothing.

SET\_TRV This program sets the I/O transfer vector to the value of the passed argument. For further information, see Section 4-16 through 4-20 and Table 4-2 in the 1802 pod manual.

Arguments: VECTOR - The value that is to be the new I/O transfer vector. Any number between O and FFFF is a legal value for this argument.

Faults : test\_aborted

reason "Illegal vector".

The value of VECTOR does not conform to the restrictions detailed above.

Returns : Nothing.

WR\_DMA\_V This program writes the passed data to the address the DMA register points to. For further information, see Section 4-21 and Table 4-2 in the 1802 pod manual.

Arguments: DATA - The value to be written to the address the DMA register points to. Any number between 0 and FF is a legal value for this argument.

Faults: test aborted

reason "Illegal data".

The value of DATA does not conform to the restrictions placed above.

Returns: Nothing.

#### SYNC MODES

| NAME                                                        | MNEMONIC                             | CODE                         |

|-------------------------------------------------------------|--------------------------------------|------------------------------|

| DMA Address Sync   DMA Data Sync   Address Sync   Data Sync | DMA_ADDR<br>DMA_DATA<br>ADDR<br>DATA | O  <br>  1  <br>  A  <br>  D |

## POD SYNC CALIBRATION DATA

| SYNC MODE                                        | UUT SIGNAL               | <br>  EDGE OF SIGNAL<br>                             | OFFSET FROM EDGE                             |

|--------------------------------------------------|--------------------------|------------------------------------------------------|----------------------------------------------|

| <br>  ADDR<br>  DATA<br>  DMA_ADDR<br>  DMA_DATA | TPA<br>TPB<br>TPA<br>TPB | <br>  FALLING<br>  FALLING<br>  FALLING<br>  FALLING | -45ns  <br>  -45ns  <br>  -45ns  <br>  -45ns |

#### **ENABLEABLE LINES**

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod timeout enabled line fault mask.

|             | BIT POSITION | MNEMONIC |

|-------------|--------------|----------|

| ~WAIT  <br> | bit 4        | ~WAIT    |

#### TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

## Fault Conditions Using the Address Mask

pod\_addr\_tied

## Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout\_enabled line

# Fault Conditions Using the Control Mask

pod\_control\_tied

# Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

----- 6502 POD -----

## NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

## POD ADDRESS SPACE OPTIONS

Only the following pod address space option is available.

SPACE

**MEMORY**

## POD-SPECIFIC SETUP INFORMATION

NONE

## AVAILABLE TL/1 SUPPORT PROGRAMS

NONE

## POD SYNC MODES

The 6502 pod always runs in a single sync mode that is sufficient for both data and address sync. However, two sync modes are provided to allow for independent calibration of the ~PODSYNC signal to the appropriate UUT signal.

| NAME                                  | <br>  MNEMONIC<br>       | <br>  CODE  <br> |

|---------------------------------------|--------------------------|------------------|

| <br>  Address Sync<br>  Data Sync<br> | <br>  ADDR<br>  DATA<br> | A  <br>  D       |

## POD SYNC CALIBRATION DATA

| SYNC MODE                | UUT SIGNAL | EDGE OF SIGNAL     | OFFSET FROM EDGE |

|--------------------------|------------|--------------------|------------------|

| <br>  ADDR<br>  DATA<br> | CLK2       | FALLING<br>FALLING | -60ns<br>-10ns   |

#### ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod\_timeout\_enabled line fault mask.

| NAME  <br> - | BIT POSITION | <br>  MNEMONIC |

|--------------|--------------|----------------|

| READY        | bit 5        | RDY            |

## TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

## Fault Conditions Using the Address Mask

pod addr tied

## Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout\_enabled\_line

## Fault Conditions Using the Control Mask

pod control tied

## Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

| <br>6800 | POD |  |

|----------|-----|--|

| 0000     | LOD |  |

## NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

## POD ADDRESS SPACE OPTIONS

Only the following pod address space option is available.

SPACE

MEMORY

## POD-SPECIFIC SETUP INFORMATION

NONE

## AVAILABLE TL/1 SUPPORT PROGRAMS

NONE

## POD SYNC MODES

The 6800 pod always runs in a single sync mode that is sufficient for both data and address sync. However, two sync modes are provided to allow for independent calibration of the PODSYNC signal to the appropriate UUT signal.

| <br>  NAME<br>                        | MNEMONIC     | CODE             |

|---------------------------------------|--------------|------------------|

| <br>  Address Sync<br>  Data Sync<br> | ADDR<br>DATA | <br>  A  <br>  D |

## POD SYNC CALIBRATION DATA

| SYNC MODE                | UUT SIGNAL | <br>  EDGE OF SIGNAL<br>       | OFFSET FROM EDGE   |

|--------------------------|------------|--------------------------------|--------------------|

| <br>  ADDR<br>  DATA<br> | PH2<br>PH2 | <br>  FALLING<br>  FALLING<br> | -25ns  <br>  -25ns |

## ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod\_timeout\_enabled\_line fault mask.

| NAME                | BIT POSITION | <br>  MNEMONIC<br> |

|---------------------|--------------|--------------------|

| THREE STATE CONTROL | bit 3        | TSC                |

| DATA BUS ENABLE     | bit 4        | DBE                |

| ~HALT               | bit 5        | HALT               |

## TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod data tied

## Fault Conditions Using the Address Mask

pod addr tied

## Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout enabled line

## Fault Conditions Using the Control Mask

pod control tied

## Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

| <br>6802 | POD |  |

|----------|-----|--|

| OOOL     | LUD |  |

## NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

## POD ADDRESS SPACE OPTIONS AVAILABLE

Only the following pod address space option is available.

SPACE

**MEMORY**

## POD-SPECIFIC SETUP INFORMATION

NONE

## AVAILABLE TL/1 SUPPORT PROGRAMS

NONE

## POD SYNC MODES

The 6802 pod always runs in a single sync mode that is sufficient for both data and address sync. However, two sync modes are provided to allow for independent calibration of the PODSYNC signal to the appropriate UUT signal.

| NAME                                  | MNEMONIC     | CODE   |

|---------------------------------------|--------------|--------|

| <br>  Address Sync<br>  Data Sync<br> | ADDR<br>DATA | A<br>D |

## POD SYNC CALIBRATION DATA

| SYNC MODE        | UUT SIGNAL | <br>  EDGE OF SIGNAL<br>       |                |

|------------------|------------|--------------------------------|----------------|

| ADDR  <br>  DATA | E<br>E     | <br>  FALLING<br>  FALLING<br> | -30ns<br>-30ns |

#### ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod timeout enabled line fault mask.

|   | NAME         | BIT POSITION | <br>  MNEMONIC  <br> |

|---|--------------|--------------|----------------------|

| 1 | MEMORY READY | bit 4        | MR                   |

|   | ~HALT        | bit 5        | ~HALT                |

## TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod data tied

## Fault Conditions Using the Address Mask

pod addr tied

## Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout\_enabled\_line

#### Fault Conditions Using the Control Mask

pod control tied

## Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

----- 6809 POD -----

#### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

#### MULTIPLE DATABASES

The 6809 pod has two modes, the 6809 mode and the 6809E mode. There is a database provided to support each of the two operational modes of this pod. The 9100 automatically detects which type of UUT is being used and loads the appropriate database for that UUT. In the following description, any differences between the databases are noted.

#### ADDRESS SPACE OPTIONS AVAILABLE

Only the following pod address space option is available.

**SPACE**

MEMORY

#### POD-SPECIFIC SETUP INFORMATION

NONE

## AVAILABLE TL/1 SUPPORT PROGRAMS

NOTE

TL/1 hexadecimal data requires a "\$" prefix character.

QWK\_RD This program may be used to put the pod in Quick Looping read mode at the address specified by the argument. For further information about Quick Looping read mode, see Section 4-4 of the 6809 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping read. Any number between 0 and FFFF

is a legal value for this argument.

10 d regal value for only diguil

Faults: test aborted

reason "Illegal address".

The ADDR argument has a value greater than FFFF.

Returns : The value that is found at the address specified by the argument during the first UUT access of the Quick

Looping read mode.

QWK\_WR

This program may be used to put the pod in Quick Looping write mode using the data and address specified by the arguments. For further information on Quick Looping write mode, refer to Section 4-4 of the 6809 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping write. Any number between 0 and FFFF is a legal value for this argument.

DATA - The data that is to be written to the address specified by the ADDR argument. Any number between 0 and FF is a legal value for this argument.

Faults: test aborted

reason "Illegal address". The ADDR argument has a value greater than FFFF.

reason "Illegal data".

The DATA argument has a value greater than FF.

Returns : Nothing.

#### POD SYNC MODES

The 6809 pod always runs in a single sync mode that is sufficient for both data and address sync. However, two sync modes are provided to allow for independent calibration of the PODSYNC signal to the appropriate UUT signal.

| <br>  NAME<br>                        | MNEMONIC     | CODE   |

|---------------------------------------|--------------|--------|

| <br>  Address Sync<br>  Data Sync<br> | ADDR<br>DATA | A<br>D |

## POD SYNC CALIBRATION DATA

The 6809 and 6809E modes both have the same calibration data.

| SYNC MODE                | UUT SIGNAL | <br>  EDGE OF SIGNAL<br>       | OFFSET FROM EDGE   |

|--------------------------|------------|--------------------------------|--------------------|

| <br>  ADDR<br>  DATA<br> | E<br>  E   | <br>  FALLING<br>  FALLING<br> | -15ns  <br>  -15ns |

#### ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod\_timeout enabled line fault mask.

6809 Mode:

| NAME                                        | <br>  BIT POSITION<br>      | <br>  MNEMONIC  <br>        |

|---------------------------------------------|-----------------------------|-----------------------------|

| <br>  ~HALT<br>  ~DMA<br>  MEMORY READY<br> | bit 1<br>  bit 4<br>  bit 5 | ~HALT  <br>  ~DMA  <br>  MR |

6809E Mode:

| NAME  <br>                  | BIT POSITION   | <br>  MNEMONIC  <br> |

|-----------------------------|----------------|----------------------|

| THREE STATE CONTROL   THALT | bit 0<br>bit 1 | TSC  <br>HALT        |

## TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

## Fault Conditions Using the Address Mask

pod\_addr\_tied

## Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout enabled line

# Fault Conditions Using the Control Mask

pod\_control\_tied

# Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

#### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

#### MULTIPLE DATABASES

The 68000 pod operates with the DIP, PGA, PLCC, and Quad Pack versions of the microprocessor. In order to support the package variations, three databases are required to support the pod. Like other pods, the 68000 pod assumes a particular package type is being used. Because of this, the user must enter the name of the required database into the 9100 series mainframe if the database for a package type other other than the default is desired.

Use the following databases with the corresponding package types.

| <br>  PACKAGE TYPE         | <br>  DATABASE TO USE<br>                     |  |

|----------------------------|-----------------------------------------------|--|

| DIP PGA LCC/PLCC Quad Pack | 68000 (default)<br>68000P<br>68000L<br>68000L |  |

To load the database for the PGA, LCC/PLCC, or Quad Pack package styles, you must press the SETUP MENU key, then the  $\rightarrow$  key, then the SOFT KEYS key. Then the POD NAME softkey must be pressed, followed by the  $\rightarrow$  key. Now you may type the name of the desired database (68000, 68000L, or 68000P) and press the ENTER key. After a short disk operation the new database will be loaded.

The 68000 database comes up when the 68000 pod is plugged into the 9100 series mainframe because the pod reports the name 68000. If you wish to change the default startup database for the 68000 pod, you may copy the desired library over the 68000 library (be sure NOT to do this to the Distribution disks). Since the 9100 looks in the 68000 library when starting up the 68000 pod, whatever is present in that library is used as the startup database. Copying over the default removes the need to go through the steps in the previous paragraph every time the mainframe is reset.

## POD ADDRESS SPACE OPTIONS

The following pod address space options are available.

|   | SPACE   | <br>  SIZE<br> |

|---|---------|----------------|

| - |         |                |

| 1 | SUPPROG | WORD           |

|   | SUPPROG | BYTE           |

|   | USRPROG | WORD           |

| 1 | USRPROG | BYTE           |

| 1 | SUPDATA | WORD           |

| 1 | SUPDATA | BYTE           |

| 1 | USRDATA | WORD           |

| 1 | USRDATA | BYTE           |

| 1 |         |                |

## POD-SPECIFIC SETUP INFORMATION

| POD SETUP                                                            | RANGE/KEY                                      | <br>  DEFAULT<br>                                                                                  | <br>  POD MANUAL REFERENCE<br>                                                                                                                                                                                               |

|----------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFLT_FC STANDBY n  <br>  DFLT_FC STANDARD n  <br>  DFLT_FC DEFAULT n | O-FFFF O-7 O-7 O-7 O-FFFF O-FFFF O-FFFF O-FFFF | A<br>  FFFF<br>  FFF<br>  O<br>  6<br>  6<br>  6<br>  FFFF<br>  4000<br>  0000<br>  4000<br>  0000 | See Section 4-32 See Section 4-44 See Section 4-45 See Section 4-30 See Section 4-36 See Section 4-34 See Section 4-38 See Section 4-35 See Section 4-37 See Section 4-47 See Section 4-47 See Section 4-48 See Section 4-49 |

## AVAILABLE TL/1 SUPPORT PROGRAMS

NOTE

TL/1 hexadecimal data requires a "\$" prefix character.

FRC\_INT This program forces the execution of an interrupt acknowledge routine at the passed Interrupt Priority Level.

Arguments: IPL - The interrupt priority level of the interrupt acknowledge cycle that is to be simulated. IPL may have any value from 1 to 7.

Faults: test aborted

reason "Illegal argument".

The value of IPL does not conform to the

requirements detailed above.

Returns: Nothing.

FRC\_RINT This program forces continuous execution of the an interrupt acknowledge routine at the passed Interrupt Priority Level.

Arguments: IPL - The interrupt priority level of the interrupt

acknowledge cycle that is to be simulated.

IPL may have any value from 1-7.

Faults: test aborted

reason "Illegal argument".

The value of IPL does not conform to the

requirements detailed above.

Returns: Nothing.

QWK\_RAM

This program embodies all of the functions of the 68000 pod Quick RAM test. For further information about the usage of the Quick RAM test, see Section 4-22 of the 68000 pod manual. The major difference between the test that the pod manual describes and the test that is implemented by the QWK\_RAM TL/1 program is that the TL/1 program only allows the Quick RAM test to be executed in the mainframe's current address space.

Arguments: ADDR - This is the starting address of the Quick RAM test. ADDR may be any numeric value between 0 and FFFFFF. ADDR's value may not be odd if the mainframe is in a WORD address space.

UPTO - This is the ending address of the Quick RAM test. UPTO may be any numeric value between 0 and FFFFFF. UPTO's value must be greater than that of ADDR and may not be odd if the mainframe is in a WORD address space.

ADDRSTEP - This is the address increment for the Quick RAM test. If ADDRSTEP has the value zero, the Quick RAM test will default to a two byte address increment. ADDRSTEP must be even if the mainframe is in a WORD address space and may not be greater than F (15 decimal).

Faults: test aborted

reason "Illegal address in invocation". This fault is included for consistency with the way 9000 series testers handle the Quick RAM program and should never be seen in normal operation.

reason "Illegal address increment". The value of the ADDRSTEP argument does not conform to the restrictions detailed above.

reason "Illegal data in invocation". This fault is included for consistency with the way 9000 series testers handle the Quick RAM program and should never be seen in normal operation.

reason "Illegal start address".

The value of the ADDR argument does not conform to the restrictions detailed above.

reason "Illegal stop address".

The value of the UPTO argument does not conform to the restrictions detailed above.

reason "New command entered".

A new command was entered during the execution of the Quick RAM test. This fault should never be raised because the program is in complete control of the mainframe while it is executing.

reason "Space not found". The current address space that the mainframe is in is not known by the program. This fault should never be raised in normal operation.

test\_failed

See the 9100-Series TL/1 Reference Manual for a list of the RAM Test Fault Conditions.

Returns: Nothing.

QWK\_RD This program places the pod in Quick Looping read mode at the passed address. For further information about Quick Looping read mode, see Section 4-21 of the 68000 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping read. Any number between 0 and FEFFFF is a legal value for this argument. ADDR's value must be even if the mainframe is ir a WORD address space.

Faults: test aborted

reason "Illegal address". The ADDR argument does not conform to the specification detailed above.

reason "Space not found". The address space that the mainframe is in as not known by the program. This fault should never be raised in normal operation.

Returns: The value that is found at the address specified by the argument during the first UUT access of the Quick Looping read mode.

QWK ROM

This program embodies all of the functions of the 68000 pod Quick ROM test. For further information about the usage of the Quick ROM test, see Section 4-23 of the 68000 pod manual. The major difference between the test that the pod manual describes and the test that is implemented by the QWK\_ROM TL/1 program is that the TL/1 program only allows the Quick ROM test to be executed in the mainframe's current address space.

Arguments: ADDR - This is the starting address of the Quick ROM test. ADDR may be any numeric value between 0 and FFFFFF. ADDR's value may not be odd if the mainframe is in a WORD address space.

UPTO - This is the ending address of the Quick ROM test. UPTO may be any numeric value between 0 and FFFFFF. UPTO's value must be greater than that of ADDR and may not be odd if the mainframe is in a WORD address space.

ADDRSTEP - This is the address increment for the Quick ROM test. If ADDRSTEP has the value zero, the Quick ROM test will default to a two byte address increment. ADDRSTEP must be even if the mainframe is in a WORD address space and may not be greater than F (15 decimal).

Faults : test\_aborted

reason "Illegal address in invocation". This fault is included for consistency with the way 9000 series testers handle the Quick ROM program and should never be seen in normal operation.

reason "Illegal address increment". The value of the ADDRSTEP argument does not conform to the restrictions detailed above.

reason "Illegal data in invocation". This fault is included for consistency with the way 9000 series testers handle the Quick ROM program and should never be seen in normal operation.

reason "Illegal start address".

The value of the ADDR argument does not conform to the restrictions detailed above.

reason "Illegal stop address".

The value of the UPTO argument does not conform to the restrictions detailed above.

reason "New command entered".

A new command was entered during the execution of the Quick ROM test. This fault should never be raised because the program is in complete control of the mainframe while it is executing.

reason "Space not found".

The current address space that the mainframe is in is not known by the program. This fault should never be raised in normal operation.

test failed

reason "Inactive bits detected".

Some set of bits has been determined to be inactive.

Slots:

Returns: A checksum of the area of memory that was tested. This checksum is unrelated to the checksum that is generated by the regular ROM test.

QWK\_WR This program may be used to put the pod in Quick Looping write mode using the data and address specified by the arguments. For further information on Quick Looping write mode, see Section 4-21 of the 68000 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping write. Any number between 0 and FFFFFF is a legal value for this argument.

ADDR's value must be even if the mainframe is in a WORD address space.

DATA - The data that is to be written to the address specified by the ADDR argument. Legal values for this argument are any number between 0 and FF if the mainframe is in a BYTE address space or any number between 0 and FFFF in a WORD address space.

Faults : test\_aborted

reason "Illegal address". The value of ADDR does not conform to the restrictions detailed above.

reason "Illegal data".

The value of DATA does not conform to the restrictions detailed above.

reason "Space not found". The current address space that the mainframe is in is not known by the program. This fault should never be raised in normal operation.

Returns : Nothing.

RD NOARM This program returns the most recent interrupt type information from the pod without re-enabling interrupts. For further information, refer to Section 4-28 of the 68000 pod manual.

Arguments: None.

Faults: None.

Returns: The interrupt type information that was stored during the last interrupt acknowledge cycle. For help interpreting the return value, see Section 4-28 in the 68000 pod manual.

RD REARM

This program returns the most recent interrupt type information from the pod and re-enables interrupts. For further information, consult Section 4-29 of the 68000 pod manual.

Arguments: None.

Faults: None.

Returns: The interrupt type information that was stored during the last interrupt acknowledge cycle. For help interpreting the return value, see Section 4-28 in the 68000 pod manual.

UUT RST

Execution of this program causes the pod to execute a RESET instruction, forcing the RESET line low for 124 clock cycles.

Arguments : None.

Faults: None.

Returns: Nothing.

#### POD SYNC MODES

| <br>  NAME<br> | <br>  MNEMONIC<br> | CODE |

|----------------|--------------------|------|

| Interrupt Sync | INTA               | 1    |

| Address Sync   | ADDR               | A    |

| Data Sync      | DATA               | D    |

# POD SYNC CALIBRATION DATA

| SYNC MODE                          | <br>  UUT SIGNAL<br>           | <br>  EDGE OF SIGNAL<br>             | OPPSET FROM EDGE            |

|------------------------------------|--------------------------------|--------------------------------------|-----------------------------|

| <br>  ADDR<br>  DATA<br>  INTA<br> | ~AS<br>  ~AS<br>  ~AS<br>  ~AS | <br>  RISING<br>  RISING<br>  RISING | -40ns<br>  -15ns<br>  -15ns |

#### **ENABLEABLE LINES**

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod\_timeout\_enabled line fault mask.

| NAME  | BIT POSITION            | <br>  MNEMONIC  <br>                   |

|-------|-------------------------|----------------------------------------|

| ~HALT | bit 0<br>bit 1<br>bit 3 | <br>  ~HALT  <br>  ~BR/~BG  <br>  INTR |

#### TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

### Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

# Fault Conditions Using the Address Mask

pod\_addr tied

### Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout\_enabled line

# Fault Conditions Using the Control Mask

pod control tied

### Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

| 8080 | POD |  |

|------|-----|--|

#### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

### POD ADDRESS SPACE OPTIONS AVAILABLE

The following pod address space options are available.

**SPACE**

**MEMORY**

I/0

### POD-SPECIFIC SETUP INFORMATION

NONE

### AVAILABLE TL/1 SUPPORT PROGRAMS

NONE

#### SYNC MODES

The 8080 pod always runs in a single sync mode that is sufficient for both data and address sync. However, two sync modes names are provided to allow for independent calibration of the PODSYNC signal to the appropriate UUT signal.

| <br>  NAME<br>                  | MNEMONIC     | CODE            |

|---------------------------------|--------------|-----------------|

| Address Sync<br>  Data Sync<br> | ADDR<br>DATA | A  <br>D  <br>L |

### POD SYNC CALIBRATION DATA

|                          |              |                    | OFFSET FROM EDGE   |

|--------------------------|--------------|--------------------|--------------------|

| SYNC MODE                | UUT SIGNAL   | EDGE OF SIGNAL     |                    |

|                          |              |                    |                    |

| <br>  ADDR<br>  DATA<br> | DBIN<br>DBIN | FALLING<br>FALLING | -90ns  <br>  -90ns |

# POD SYNC CALIBRATION DATA

| SYNC MODE                | UUT SIGNAL   | <br>  EDGE OF SIGNAL<br> | OFFSET FROM EDGE |

|--------------------------|--------------|--------------------------|------------------|

| <br>  ADDR<br>  DATA<br> | DBIN<br>DBIN | FALLING<br>FALLING       | -90ns<br>-90ns   |

# ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod\_timeout\_enabled line fault mask.

| <br>  NAME   | BIT POSITION   | <br>  MNEMONIC<br> |

|--------------|----------------|--------------------|

| READY   HOLD | bit 4<br>bit 5 | READY<br>HOLD      |

### TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from  $\mathop{\mathrm{pod}}\nolimits$  operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

# Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

# Fault Conditions Using the Address Mask

pod\_addr\_tied

# Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout enabled line

### Fault Conditions Using the Control Mask

pod\_control\_tied

# Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

----- 8085 POD -----

### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

### POD ADDRESS SPACE OPTIONS

The following pod address space options are available.

SPACE

MEMORY

I/0

### POD-SPECIFIC SETUP INFORMATION

NONE

### AVAILABLE TL/1 SUPPORT PROGRAMS

NONE

### POD SYNC MODES

| <br> <br> <br> | NAME                    | <br>  MNEMONIC<br>       | <br>  CC<br> | )DE    |

|----------------|-------------------------|--------------------------|--------------|--------|

|                | ddress Sync<br>ata Sync | <br>  ADDR<br>  DATA<br> |              | A<br>D |

### POD SYNC CALIBRATION DATA

| SYNC MODE                | <br>  UUT SIGNAL<br> | <br>  EDGE OF SIGNAL<br>  |  |

|--------------------------|----------------------|---------------------------|--|

| <br>  ADDR<br>  DATA<br> | ALE<br>  ~RD<br>     | <br>  FALLING<br>  RISING |  |

#### ENABLEABLE LINES

The mnemonics below are used in the TL/1 podsetup 'enable' statement. The bit positions correspond to bit positions in the pod timeout enabled line fault mask.

| <br>  NAME<br> | BIT POSITION | <br>  MNEMONIC<br> |

|----------------|--------------|--------------------|

| READY          | bit O        | READY              |

| HOLD           | bit 1        | HOLD               |

### TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

### Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod\_data\_tied

### Fault Conditions Using the Address Mask

pod addr tied

### Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout enabled line

#### Fault Conditions Using the Control Mask

pod control tied

### Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

----- 8048 POD -----

NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

### MULTIPLE DATABASES

The 8048 pod requires multiple databases to function properly with the many different microcomputers that the pod supports. The four pod-reported names described in the pod manual each correspond to a separate database/program set in 9100 series mainframes. The pod-reported names and their 9100 series equivalents are:

| <br>  POD-REPORTED NAME<br> | 9100 SERIES DATABASE NAME  <br> |

|-----------------------------|---------------------------------|

| '35/48                      | 3548                            |

| '39/49                      | 3949                            |

| '40/50                      | 4050                            |

| 8041                        | 8041                            |

9100 series mainframes are able to use the pod-reported name to load the appropriate database. Important differences among the databases are noted in the Section below.

### POD ADDRESS SPACE OPTIONS AVAILABLE

The following pod address space options are available.

3548, 3949, and 4050 Databases:

| SPACE                                 | <br>  RAMTYPE<br>              | PORTTYPE |

|---------------------------------------|--------------------------------|----------|

| <br>PROGRAM DATA DATA POD_RAM I/O I/O | <br>  INT_MPU<br>  EXT_UUT<br> | <br>     |

8041 Database:

| 1 | SPACE              | PORTTYPE |

|---|--------------------|----------|

| - | INT_RAM<br>POD_RAM | PORT     |

|   | I/O                | EXP_PORT |

### POD DATA SIGNAL DEFINITIONS FOR FAULT MAPPING

The following describes the non-standard mapping of specific 8048 pod data signals to fault masks for the purpose of invoking built-in 9100 fault handlers or raising built-in 9100 fault messages. In the format examples which follow bits labeled "0" are not used in the mapping but must be "0" regardless. Those labeled "X" correspond to mapped signals and are set to "0" to specify "no fault" or to "1" when a fault is to be reported.

# Address Signal Mapping to Fault Masks (8041 Mode Only)

Address signal fault mask format:

Address signal fault mask bit assignments:

| MASK<br>  BIT            | <br>  POD<br>  SIGNAL<br> | <br>  8041<br>  PIN NO. |

|--------------------------|---------------------------|-------------------------|

| 0<br>  :<br>  7          | <br>  unused<br>          |                         |

| 8<br>  9<br>  10<br>  11 | P20<br>P21<br>P22<br>P23  | 21<br>22<br>23<br>24    |

| 12<br>  :<br>  63        | unused                    |                         |

# Data Signal Mapping to Fault Masks (8048 and 8041 Modes)

Data signal fault mask format:

Data signal fault mask bit assignments:

| MASK<br>  BIT | <br>  POD<br>  SIGNAL<br>                                                                                                                              | <br>  PROCESSOR<br>  PIN NO.                                                                                                                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | DB0   DB1   DB2   DB3   DB4   DB5   DB6   DB7   P10   P11   P12   P13   P14   P15   P16   P17   P20   P21   P22   P23   P24   P25   P26   P27   unused | 12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>21<br>22<br>23<br>24<br>35<br>36<br>37<br>38 |

# POD-SPECIFIC SETUP INFORMATION

3548, 3949, and 4050 Databases:

| POD SETUP             | RANGE/KEY     | DEFAULT | <br>  POD MANUAL REFERENCE<br> |   |

|-----------------------|---------------|---------|--------------------------------|---|

| <br>  TO_LINE key<br> | INPUT/CLK_OUT | INPUT   | <br>  See Section 4-17<br>     | 1 |

8041 Database:

NONE

### AVAILABLE TL/1 SUPPORT PROGRAMS

NOTE

TL/1 hexadecimal data requires a "\$" prefix character.

QWK\_RD This program may be used to put the pod in Quick Looping read mode at the address specified by the argument. For further information about Quick Looping read mode, see the 8048 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping read. Legal values for this argument are:

3548, 3949, 4050 Modes:

PROGRAM Space - 0 through FFF.

DATA EXT\_UUT Space - 0 through FF.

I/O PORT - 0 through 2.

I/O EXP\_PORT Space - 4 through 7.

8041 Mode:

I/O PORT - 0 through 2.

I/O EXP\_PORT Space - 4 through 7.

Faults: test aborted

reason "Illegal address".

The ADDR argument does not conform to the

restrictions placed above.

reason "Illegal space".

The current address space is not legal for

this test.

reason "Space not found".

The current address space that the mainframe is in is not known by the program. This fault should never be raised in normal operation.

Returns: The value that is found at the address specified by the argument during the first UUT access of the Quick Looping read mode.

This program may be used to put the pod in Quick Looping write mode using the data and address specified by the arguments. For further information on Quick Looping write mode, refer to the 8048 pod manual.

Arguments: ADDR - The address at which to perform the Quick Looping read. Legal values for this argument are:

3548, 3949, 4050 Modes:

DATA EXT\_UUT Space - 0 through FF.

I/O PORT - 0 through 2.

I/O EXP\_PORT Space - 4 through 7.

8041 Mode:

I/O PORT - 0 through 2. I/O EXP PORT Space - 4 through 7.

DATA - The data that is to be written to the address specified by the ADDR argument. Any number between 0 and FF is a legal value for this argument (0 - F for I/O EXP PORT space).

Faults: test aborted

reason "Illegal address". The ADDR argument does not conform to the restrictions placed above.

reason "Illegal data". The DATA argument does not conform to the restrictions placed above.

reason "Illegal space". The current address space is not legal for this test.

reason "Space not found".

The current address space that the mainframe is in is not known by the program. This fault should never be raised in normal operation.

Returns: Nothing.

#### SYNC MODES

| NAME                                  | <br>  MNEMONIC<br>       | <br>  CODE  <br> |

|---------------------------------------|--------------------------|------------------|

| <br>  Address Sync<br>  Data Sync<br> | <br>  ADDR<br>  DATA<br> | <br>  A  <br>  D |

### POD SYNC CALIBRATION DATA

All 8048 pod modes have the same calibration data.

| SYNC MODE                           |            |                |                  |

|-------------------------------------|------------|----------------|------------------|

|                                     | UUT SIGNAL | EDGE OF SIGNAL | OFFSET FROM EDGE |

|                                     |            |                |                  |

|                                     |            |                |                  |

| ADDR                                | ALE        | FALLING        | -45ns            |

| DATA                                | ~RD*       | RISING         | -45ns            |

| * PROG signal is used in 8041 mode. |            |                |                  |

#### **ENABLEABLE LINES**

NONE

### TL/1 FAULT CONDITIONS

This section lists the TL/1 fault conditions that can result from pod operation.

Handlers for most fault conditions are based on one of the 4 mask types: address, data, status, or control. See the Programmer's Information in the Introduction of this manual for information about the format of each fault mask.

## Fault Conditions Using the Data Mask

pod\_data\_incorrect

pod data tied

### Fault Conditions Using the Address Mask

pod addr tied

### Fault Conditions Using the Status Mask

pod\_forcing\_active

pod\_interrupt\_active

pod\_timeout enabled line

### Fault Conditions Using the Control Mask

pod control tied

### Fault Conditions With No Fault Mask

pod\_timeout\_bad\_pwr

pod\_timeout\_no\_clk

pod\_timeout\_recovered

pod\_timeout\_setup

pod\_uut\_power

----- 8051 POD -----

#### NOTE

Read the Introduction section for important information needed to operate and program this pod with the 9100 series mainframes.

### MULTIPLE DATABASES

The 8051 pod requires multiple databases to function properly with the many different microcomputers that the pod supports. The three pod-reported names described in the pod manual each correspond to a separate database/program set in 9100 series mainframes. The pod-reported names and their 9100 series equivalents are:

| <br>  POD-REPORTED NAME  <br> | 9100 SERIES DATABASE NAME |

|-------------------------------|---------------------------|

| 8031                          | 8031                      |

| 8051                          | 8051                      |

| 8051X                         | 8051X                     |

9100 series mainframes are able to use the pod-reported name to load the appropriate database. Important differences among the databases are noted in the Section below.

#### POD ADDRESS SPACE OPTIONS AVAILABLE

The following pod address space options are available.

| SPACE                                                                             | <br>  BIT_TYPE<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>  BIT_REG                                   |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| EXT_PRG EXTDAT16 EXT_DAT8 INT_DAT SFR_REG BIT | FLAG   FLAG   REGISTER   REGIST | PO   P1   P2   P3   TCON   SMOD   IE   IP   PSW |

### POD ADDRESS SPACE OPTIONS AVAILABLE (CONT)

| <br>  SPACE<br>                     | BIT_TYPE                         | BIT_REG  |

|-------------------------------------|----------------------------------|----------|

| <br>  BIT<br>  BIT<br>  INT_PRG<br> | <br>  REGISTER<br>  REGISTER<br> | ACC<br>B |

### POD DATA SIGNAL DEFINITIONS FOR FAULT MAPPING